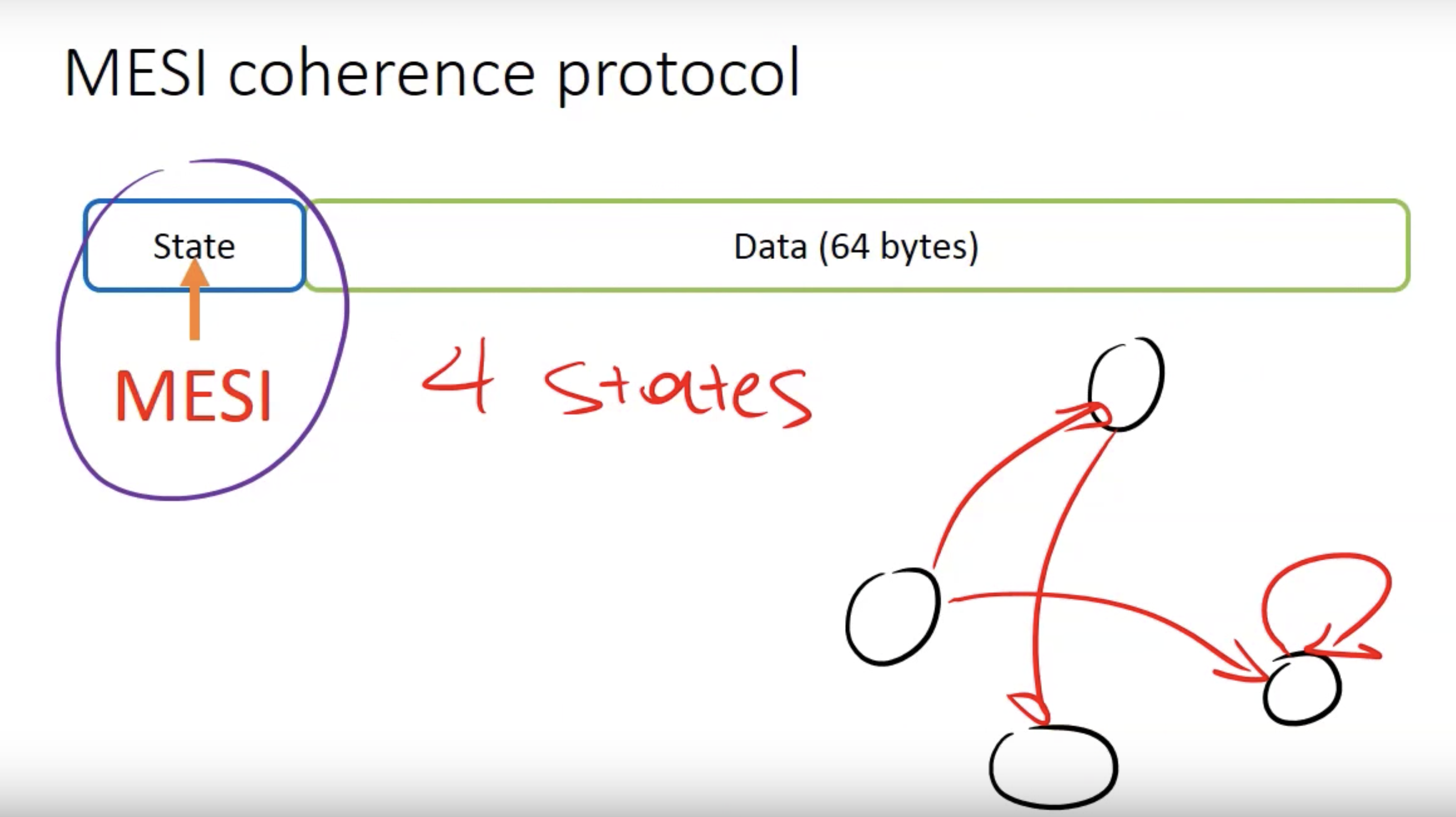

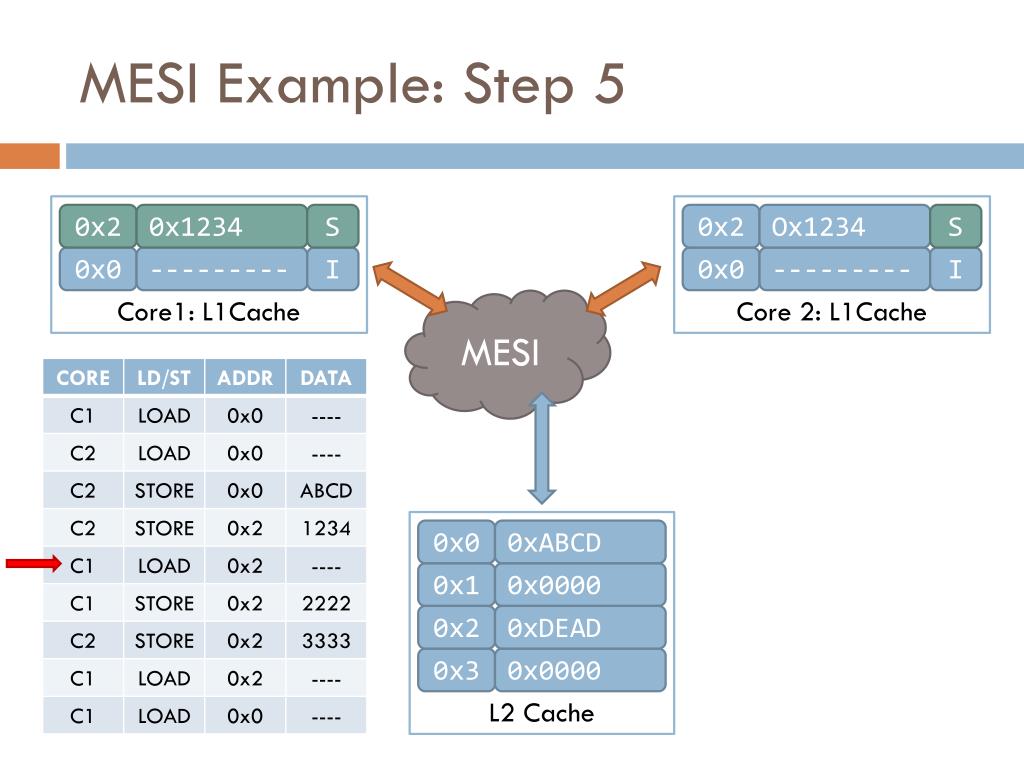

Open2C reduces the amount of effort researches spend on system implementation – allowing them to focus on the protocol itself or a separate unit optimization. If a cacheline is in E state, that tells the requesting processor that one (and only one) other processor has a copy of this line. The generated system can be simulated using existing Chisel-based simulation tools or be compiled into the RTL and placed on FPGA for further evaluation. The MESI protocol is a cache-coherence protocol that ensures each core/processor gets the most up-to-date data from other processors cache (or mem) when requested. Invalid - Line data is not valid (as in simple cache) MESI Protocol (3) Cache line changes state as a function of memory access events.

#MESI CACHE COHERENCE GENERATOR#

The Open2C generator is written in Chisel language that allows each component to be accessed through provided methods in a functional and modular way. (multiprocessor ‘dirty’) Exclusive - cache line is the same as main memory and is the only cached copy Shared - Same as main memory but copies may exist in other caches. Open2C includes a library of basic parameterized components that are required to build a complex coherent cache memory subsystem, such as miss register, TAG array, replacement policy unit, etc. The project aims to provide a powerful yet flexible and easy-to-extend tool that enables exploring coherent cache memory subsystem for upcoming large-scale computing systems. We present Open Cache Coherence (Open2C). The L1 cache controller can however be altered to any coherence protocol.There may also be a. Existing evaluation techniques, such as cycle-approximate estimation or cycle-accurate simulation, do not guarantee accurate and fast results in the first case or require tremendous amount of efforts to implement and modify the system in the second. The baseline model includes MSI and MESI cache coherence protocols. However, due to extensive protocol-related traffic and lack of explicit data movement management, cache memory scalability becomes a big concern. Being managed by hardware, the cache subsystem facilitates multi-core system programming and allows developers to focus on other crucial aspects. It maintains memory consistency across on-chip caches that hide the memory latency to improve computational performance.

A cache-coherent memory subsystem plays an important role in complex digital computing systems.

0 kommentar(er)

0 kommentar(er)